Σ' αυτό το άρθρο θα δούμε την κατασκευή ενός συχνομέτρου τεσσάρων ψηφίων, κατασκευασμένο με το CPLD XC95108 της Xilinx. Βασίζεται στο starter kit που δημοσίευσα στο προηγούμενο άρθρο και έχει υλοποιηθεί με σχηματικό διάγραμμα ενώ τα modules είναι γραμμένα σε Verilog. Χρησιμοποιεί ακριβώς το 50% των καταχωρητών του chip, επομένως άνετα θα μπορούσε να επεκταθεί στα 8 ψηφία. Το chip που χρησιμοποίησα έχει propagation delay 15ns, πράγμα που μας περιορίζει την μέγιστη συχνότητα περίπου στα 70 MHz. Φυσικά με την χρήση ενός prescaler θα μπορούσαμε να αυξήσουμε την συχνότητα εισόδου σε αρκετά GHz.

Σ' αυτό το άρθρο θα δούμε την κατασκευή ενός συχνομέτρου τεσσάρων ψηφίων, κατασκευασμένο με το CPLD XC95108 της Xilinx. Βασίζεται στο starter kit που δημοσίευσα στο προηγούμενο άρθρο και έχει υλοποιηθεί με σχηματικό διάγραμμα ενώ τα modules είναι γραμμένα σε Verilog. Χρησιμοποιεί ακριβώς το 50% των καταχωρητών του chip, επομένως άνετα θα μπορούσε να επεκταθεί στα 8 ψηφία. Το chip που χρησιμοποίησα έχει propagation delay 15ns, πράγμα που μας περιορίζει την μέγιστη συχνότητα περίπου στα 70 MHz. Φυσικά με την χρήση ενός prescaler θα μπορούσαμε να αυξήσουμε την συχνότητα εισόδου σε αρκετά GHz.

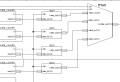

Βεβαίως το συχνόμετρο θα μπορούσε να κατασκευαστεί με ένα microcontroller και θα είχε και περισσότερες δυνατότητες, αλλά στη συγκεκριμένη κατασκευή θέλουμε να εμβαθύνουμε στον προγραμματισμό CPLD και FPGA. Στο σχήμα 1 βλέπουμε το εσωτερικό διάγραμμα που σχεδιάστηκε με το ISE και παρουσιάζει την σύνδεση των διάφορων modules.

|

|

| Σχήμα 1 |

Εικόνα 2 |

Ο divider δέχεται clock συχνότητας 31250 Hz και παράγει διάφορες τετραγωνικές κυματομορφές για την λειτουργία του συχνόμετρου όπως τα σήματα dig0 και dig1 που κάνουν την πολυπλεξία και σάρωση του display, τα clkout1 και clkout2 που μαζί με τις τριπλές AND και τις δύο NOT, παράγουν το σήμα πύλης 1sec και τα σήματα για Latch και μετά Reset των μετρητών. Το σήμα rst είναι άχρηστο και χρησιμοποιείται μόνο στην εξομοίωση.

Η βασική θεωρεία των συχνομέτρων είναι το άνοιγμα της πύλης (AND2) για 1 δευτερόλεπτο και στο χρόνο αυτό μετράμε πόσοι παλμοί πέρασαν αφού αυτοί καταμετρούνται από τους απαριθμητές. Με το πέρας του παλμού πύλης σταματάει η καταμέτρηση και μέσα στο επόμενο δευτερόλεπτο θα απομνημονευθεί το περιεχόμενο των δεκαδικών απαριθμητών στα 4 Latch και μετά οι μετρητές θα μηδενιστούν ώστε να είναι έτοιμοι για το επόμενο άνοιγμα της πύλης.

Ο mux είναι πολυπλέκτης 4 εισόδων με 4 bit έκαστη που βγάζει ένα - ένα τα ψηφία με συχνότητα 61Hz ώστε να γίνει η σάρωση. Ο bcd2ss είναι ένας αποκωδικοποιητής από bcd σε 7 segment display για την οδήγηση των ψηφίων 7 τμημάτων. Ο dec2to4 είναι ένας αποκωδικοποιητής από 2bit σε 4 για την οδήγηση και ενεργοποίηση του κάθε ψηφίου 7 τμημάτων. Το σήμα mov είναι υπερχείλιση και ανάβει ένα led όταν το αποτέλεσμα της μέτρησης δεν εμφανίζεται ολόκληρο στην οθόνη.

Στην εικόνα 1 στην αρχή του άρθρου βλέπουμε το συχνόμετρο να μετράει σήμα συχνότητας 3907 Hz. Στην εικόνα 2 βλέπουμε τις συνδέσεις του starter kit. Προσοχή εδώ, τα σύρματα είναι πηνίου δηλαδή μονωμένα.

Παρακάτω ακολουθεί ο κώδικας των modules σε verilog και το αρχείο ucf που περιγράφει σε ποιο pin συνδέεται το κάθε σήμα.

| Ο κώδικας των modules σε verilog (fc1.v) |

Το αρχείο ucf για συσκευασία TQFP100 (fc1.ucf) |

|

|

| Δείτε το συχνόμετρο σε λειτουργία |

Κατεβάστε από εδώ τα αρχεία κατασκευής του συχνομέτρου.

(c)2010 Σταύρος Σ. Φώτογλου SV6GMP