Εδώ θα παρουσιάσω την κατασκευή μιας πλακέτας μικροελεγκτή η οποία σχεδιάστηκε για τον έλεγχο PLL σε τηλεοπτικούς πομπούς και αναμεταδότες. Η πλακέτα αυτή κατασκευάστηκε το 1997 με τον οκτάμπιτο microcontroller AVR AT90S1200 της Atmel και το αρχικό πρόγραμμα ήταν γραμμένο σε Assembly. Αργότερα τον αντικατέστησα με τον συμβατό σε συσκευασία και θέσεις ακίδων AT90S2313 , και το πρόγραμμα γράφτηκε σε C. Με αυτόν τον μικροελεγκτή χρησιμοποίησα την ίδια πλακέτα για έλεγχο πομποδεκτών NBFM που θα παρουσιάσω σε επόμενο άρθρο.

Εδώ θα παρουσιάσω την κατασκευή μιας πλακέτας μικροελεγκτή η οποία σχεδιάστηκε για τον έλεγχο PLL σε τηλεοπτικούς πομπούς και αναμεταδότες. Η πλακέτα αυτή κατασκευάστηκε το 1997 με τον οκτάμπιτο microcontroller AVR AT90S1200 της Atmel και το αρχικό πρόγραμμα ήταν γραμμένο σε Assembly. Αργότερα τον αντικατέστησα με τον συμβατό σε συσκευασία και θέσεις ακίδων AT90S2313 , και το πρόγραμμα γράφτηκε σε C. Με αυτόν τον μικροελεγκτή χρησιμοποίησα την ίδια πλακέτα για έλεγχο πομποδεκτών NBFM που θα παρουσιάσω σε επόμενο άρθρο.

Στην εικόνα 1 βλέπουμε μονταρισμένη την πλακέτα του μικροελεγκτή. Περιέχει, εκτός από τον AVR, δύο 7 segment displays για την απεικόνιση των καναλιών και σύντομων μηνυμάτων, τέσσερα push buttons για είσοδο καναλιών - προγραμμάτων και αποθήκευση στη μνήμη, έξοδο σειριακού διαύλου IIC bus για σύνδεση με τα PLL και έναν σταθεροποιητή 5V για την τροφοδοσία της πλακέτας. Στην εικόνα 2 βλέπουμε πλευρά του χαλκού της μονταρισμένης πλακέτας.

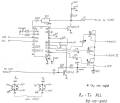

Στο σχήμα 1 βλέπουμε το θεωρητικό κύκλωμα της πλακέτας του μικροελεγκτή. Ο μικροελεγκτής χρονίζεται στα 4MHz. Η πόρτα Β είναι έξοδος και βγάζει τα πολυπλεγμένα δεδομένα για την οδήγηση των καθόδων των 7 segment displays. Τα PD0 και PD1 είναι έξοδοι και χρησιμοποιούνται για την πολυπλεξία του display και του πληκτρολογίου. Τα PD2 και PD3 είναι εισόδοι και δέχονται τα πολυπλεγμένα δεδομένα του πληκτρολογίου. Οι PD5 και PD6 είναι τα σήματα SCL και SDA για την αποστολή και λήψη πληροφοριών στα PLL. Το όλο κύκλωμα τροφοδοτείται με τάση 5V από τον σταθεροποιητή 7805.

Στο σχήμα 2 φαίνεται το θεωρητικό κύκλωμα του PLL. Χρησιμοποιώ το SDA3202 της Siemens αλλά μπορεί να χρησιμοποιηθεί και το αντίστοιχο TSA5510 της Philips. Το σήμα υψηλής συχνότητας από τον τοπικό ταλαντωτή του tuner ή τον ταλαντωτή του πομπού, εισάγεται στο transistor BR91A το οποίο ενισχύει και απομονώνει το σήμα πριν αυτό εισαχθεί στο pin 15 του ολοκληρωμένου. Πρέπει να ανοίξουμε το tuner να εντοπίσουμε τον τοπικό ταλαντωτή και να πάρουμε το σήμα υψηλής συχνότητας με χαλαρή σύζευξη ώστε να μην φορτώνουμε τον ταλαντωτή. Αν το tuner έχει μέσα prescaler τότε είναι πιο εύκολο, βγάζουμε το prescaler και παίρνουμε σήμα από την είσοδο του prescaler.

Το pin 10 (P3) καθορίζει την διεύθυνση του chip για το πρωτόκολλο IIC bus, για πομπό και δέκτη. Αν το PLL χρησιμοποιείται σε δέκτη τότε βάζουμε και τα 3 PNP transistors BC557 για την επιλογή μπάντας του tuner. Το NPN transistor BC547 που συνδέεται στο pin 18 μαζί με τα τριγύρω εξαρτήματα, συνθέτουν το low pass φίλτρο του βρόγχου. Στον συλλέκτη του transistor έχουμε την τάση συντονισμού Vt η οποία πάει στην δίοδο varicap του τοπικού ταλαντωτή.

Στην εικόνα 3 βλέπουμε την μονταρισμένη πλακέτα του PLL.

Το θεωρητικό κύκλωμα του ταλαντωτή UHF φαίνεται στο σχήμα 3. Το πρώτο transistor BFR91A μαζί με τα τριγύρω εξαρτήματα συνθέτει ένα ταλαντωτή colpitts που μπορεί να λειτουργήσει στην περιοχή από 470 έως 900 MHz. Το trimer 1-20pF σε σειρά με το πηνίο αλλάζει την περιοχή λειτουργίας του ταλαντωτή, ώστε να συντονίζει με χαμηλότερη τάση συντονισμού (12V) και με μία δίοδο varicap. Το δεύτερο BFR91A είναι ενισχυτής - buffer ικανός να οδηγήσει τις επόμενες βαθμίδες.

Στην εικόνα 5 βλέπουμε το PLL και τον ταλαντωτή του πομπού συναρμολογημένα μέσα στο ίδιο κουτί. Στην εικόνα 6 φαίνεται το εξωτερικό του ταλαντωτή - PLL. Στον συνδετήρα DIN συνδέονται τα σήματα IIC bus οι τάσεις τροφοδοσίας 12V και 5V. Το σήμα υψηλής συχνότητας βγαίνει από τον θηλυκό συνδετήρα τύπου 'F' .

Ακολουθεί το πρόγραμμα σε γλώσσα Assembly και το αρχείο προγραμματισμού της rom σε format Intel Hex. Το συγκεκριμένο πρόγραμμα είναι γραμμένο για συστήματα με μέση συχνότητα 38,9 MHz στον δέκτη και τον πομπό, γι' αυτό ο ταλαντωτής βγάζει υψηλότερη συχνότητα κατά 38,9 MHz.

|

Το πρόγραμμα του microcontroller σε Assembly (SYN1I.ASM) |

Το αρχείο της Flash Rom σε γλώσσα μηχανής (SYN1I.HEX) |

|

|

| Δείτε το σύστημα σε λειτουργία |

Στο video βλέπουμε την πλακέτα συνδεδεμένη σε δύο PLL, εκπομπής και λήψης. Το σύστημα λήψης θα παρουσιαστεί σε επόμενο άρθρο.

Κατεβάστε εδώ όλα τα αρχεία κατασκευής (τυπωμένα κυκλώματα, σχέδια, προγράμματα).

(c) 1997 Σταύρος Σ. Φώτογλου (SV6GMP)