Σ”

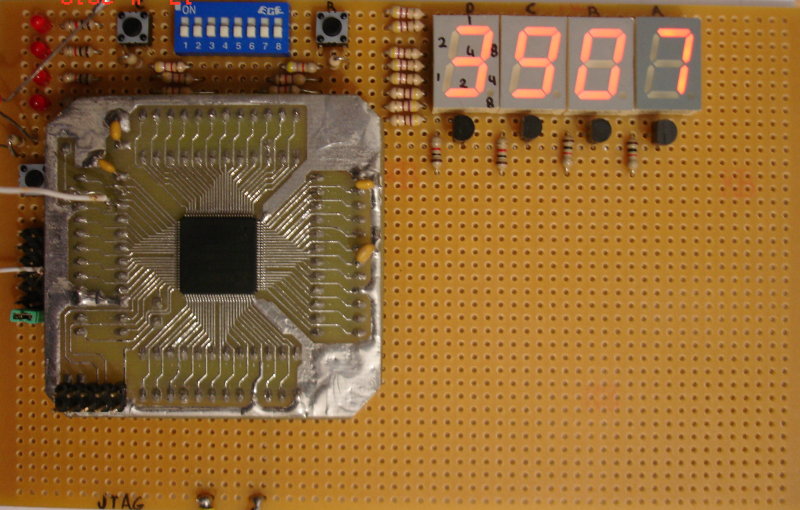

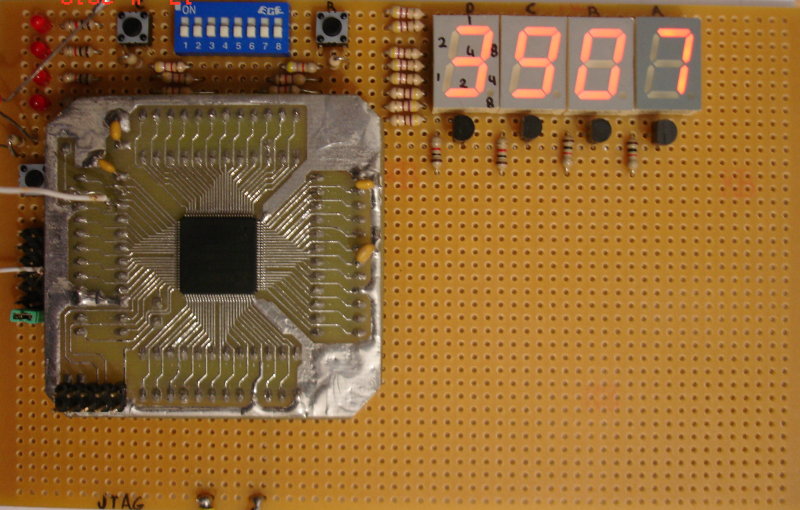

Σ” αυτό το άρθρο θα δούμε την κατασκευή ενός συχνομέτρου τεσσάρων ψηφίων, κατασκευασμένο με το CPLD XC95108 της Xilinx. Βασίζεται στο starter kit που δημοσίευσα στο προηγούμενο άρθρο και έχει υλοποιηθεί με σχηματικό διάγραμμα ενώ τα modules είναι γραμμένα σε Verilog. Χρησιμοποιεί ακριβώς το 50% των καταχωρητών του chip, επομένως άνετα θα μπορούσε να επεκταθεί στα 8 ψηφία. Το chip που χρησιμοποίησα έχει propagation delay 15ns, πράγμα που μας περιορίζει την μέγιστη συχνότητα περίπου στα 70 MHz. Φυσικά με την χρήση ενός prescaler θα μπορούσαμε να αυξήσουμε την συχνότητα εισόδου σε αρκετά GHz.

Συνέχεια →

Just another WordPress site

Σ” αυτό το άρθρο θα δούμε την κατασκευή ενός συχνομέτρου τεσσάρων ψηφίων, κατασκευασμένο με το CPLD XC95108 της Xilinx. Βασίζεται στο starter kit που δημοσίευσα στο προηγούμενο άρθρο και έχει υλοποιηθεί με σχηματικό διάγραμμα ενώ τα modules είναι γραμμένα σε Verilog. Χρησιμοποιεί ακριβώς το 50% των καταχωρητών του chip, επομένως άνετα θα μπορούσε να επεκταθεί στα 8 ψηφία. Το chip που χρησιμοποίησα έχει propagation delay 15ns, πράγμα που μας περιορίζει την μέγιστη συχνότητα περίπου στα 70 MHz. Φυσικά με την χρήση ενός prescaler θα μπορούσαμε να αυξήσουμε την συχνότητα εισόδου σε αρκετά GHz.

Σ” αυτό το άρθρο θα δούμε την κατασκευή ενός συχνομέτρου τεσσάρων ψηφίων, κατασκευασμένο με το CPLD XC95108 της Xilinx. Βασίζεται στο starter kit που δημοσίευσα στο προηγούμενο άρθρο και έχει υλοποιηθεί με σχηματικό διάγραμμα ενώ τα modules είναι γραμμένα σε Verilog. Χρησιμοποιεί ακριβώς το 50% των καταχωρητών του chip, επομένως άνετα θα μπορούσε να επεκταθεί στα 8 ψηφία. Το chip που χρησιμοποίησα έχει propagation delay 15ns, πράγμα που μας περιορίζει την μέγιστη συχνότητα περίπου στα 70 MHz. Φυσικά με την χρήση ενός prescaler θα μπορούσαμε να αυξήσουμε την συχνότητα εισόδου σε αρκετά GHz.

Σ” αυτό το άρθρο θα δούμε την κατασκευή ενός συχνομέτρου τεσσάρων ψηφίων, κατασκευασμένο με το CPLD XC95108 της Xilinx. Βασίζεται στο starter kit που δημοσίευσα στο προηγούμενο άρθρο και έχει υλοποιηθεί με σχηματικό διάγραμμα ενώ τα modules είναι γραμμένα σε Verilog. Χρησιμοποιεί ακριβώς το 50% των καταχωρητών του chip, επομένως άνετα θα μπορούσε να επεκταθεί στα 8 ψηφία. Το chip που χρησιμοποίησα έχει propagation delay 15ns, πράγμα που μας περιορίζει την μέγιστη συχνότητα περίπου στα 70 MHz. Φυσικά με την χρήση ενός prescaler θα μπορούσαμε να αυξήσουμε την συχνότητα εισόδου σε αρκετά GHz.

Σ” αυτό το άρθρο θα δούμε την κατασκευή ενός συχνομέτρου τεσσάρων ψηφίων, κατασκευασμένο με το CPLD XC95108 της Xilinx. Βασίζεται στο starter kit που δημοσίευσα στο προηγούμενο άρθρο και έχει υλοποιηθεί με σχηματικό διάγραμμα ενώ τα modules είναι γραμμένα σε Verilog. Χρησιμοποιεί ακριβώς το 50% των καταχωρητών του chip, επομένως άνετα θα μπορούσε να επεκταθεί στα 8 ψηφία. Το chip που χρησιμοποίησα έχει propagation delay 15ns, πράγμα που μας περιορίζει την μέγιστη συχνότητα περίπου στα 70 MHz. Φυσικά με την χρήση ενός prescaler θα μπορούσαμε να αυξήσουμε την συχνότητα εισόδου σε αρκετά GHz.