Παλιότερα (89-90) είχα ασχοληθεί λίγο με PAL – GAL για να βάλω κάποια εξειδικευμένη λογική σε chips. Εκείνη την εποχή ο αριθμός των πυλών και φλίπ-φλόπ ήταν μικρός και ο μόνος λόγος χρήσης τέτοιων chip ήταν το κλείδωμα του hardware παρά η οικονομία σε διακριτά ολοκληρωμένα κυκλώματα. Στα χρόνια που πέρασαν δημιουργήθηκαν μεγάλες εταιρίες όπως η Xilinx , Altera , Lattice που έφτασαν την τεχνολογία αυτών των chip σε απίστευτα επίπεδα. Σήμερα μιλάμε για chip με 200000 πύλες που μέσα μπορούν να χωρέσουν δύο πυρήνες επεξεργαστών π.χ. ARM μαζί με τα βοηθητικά περιφερειακά. Αυτά γίνονται στα FPGA που θα δούμε σε επόμενο άρθρο. Εδώ θα δούμε τα πιο απλά και μικρότερα cplds. Αρχικά αποφάσισα να μην χρησιμοποιήσω κάποιο starter kit ή αναπτυξιακό σύστημα που πουλάνε οι εταιρίες, αλλά να τα κατασκευάσω όλα μόνος μου.

Παλιότερα (89-90) είχα ασχοληθεί λίγο με PAL – GAL για να βάλω κάποια εξειδικευμένη λογική σε chips. Εκείνη την εποχή ο αριθμός των πυλών και φλίπ-φλόπ ήταν μικρός και ο μόνος λόγος χρήσης τέτοιων chip ήταν το κλείδωμα του hardware παρά η οικονομία σε διακριτά ολοκληρωμένα κυκλώματα. Στα χρόνια που πέρασαν δημιουργήθηκαν μεγάλες εταιρίες όπως η Xilinx , Altera , Lattice που έφτασαν την τεχνολογία αυτών των chip σε απίστευτα επίπεδα. Σήμερα μιλάμε για chip με 200000 πύλες που μέσα μπορούν να χωρέσουν δύο πυρήνες επεξεργαστών π.χ. ARM μαζί με τα βοηθητικά περιφερειακά. Αυτά γίνονται στα FPGA που θα δούμε σε επόμενο άρθρο. Εδώ θα δούμε τα πιο απλά και μικρότερα cplds. Αρχικά αποφάσισα να μην χρησιμοποιήσω κάποιο starter kit ή αναπτυξιακό σύστημα που πουλάνε οι εταιρίες, αλλά να τα κατασκευάσω όλα μόνος μου.

Αρχικά χρησιμοποίησα τα chip της xilinx σειρά XC95xx και συγκεκριμένα το XC95108 που έχει 108 macrocells και 2400 πύλες. Αυτά υπάρχουν σε διάφορες συσκευασίες. Εδώ χρησιμοποιώ δύο, την PC84 που είναι αρκετά μεγάλη και εύκολη στο κόλλημα και την TQFP100 που είναι πολύ μικρότερη και θα μας ταλαιπωρήσει αρκετά. Αυτά τα αγοράζουμε από την Furnell , RS , Digikey και ίσως να τα βρείτε και στην Ελλάδα. Το κόστος αγοράς είναι 12 – 15 ? το τεμάχιο ανάλογα με την συσκευασία το propagation delay και τον προμηθευτή. Πιο φτηνά είναι σε χώρες εκτός Ε.Ε. αλλά πάντα να υπολογίζετε πιθανό εκτελωνισμό.

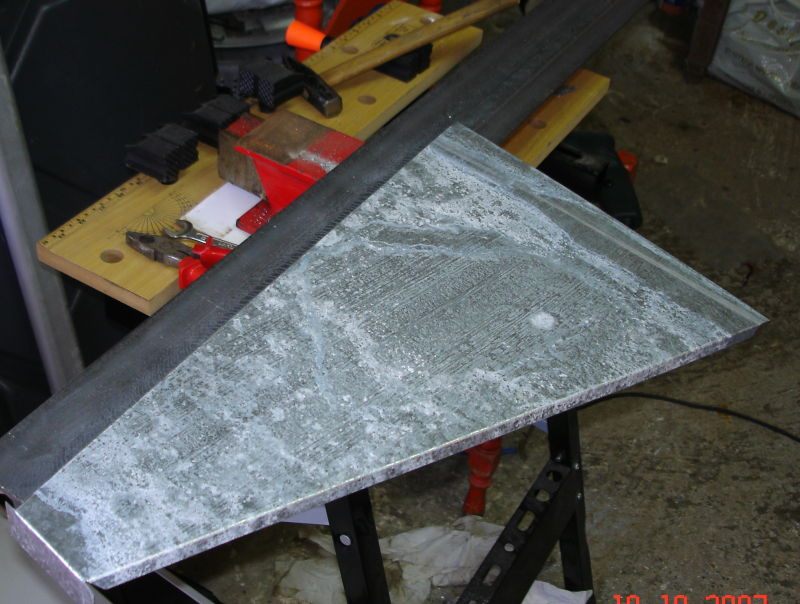

Για την κατασκευή πρωτοτύπων θα κατασκευάσουμε ένα μετατροπέα από την συσκευασία του CPLD (PC84 και TQFP100) σε βάσεις συμβατικών chip 3/10, ώστε να τα κολλάμε εύκολα σε διάτρητες πλακέτες. Αν και υπάρχουν έτοιμοι τέτοιοι μετατροπείς, εγώ έφτιαξα δύο. Είναι σχεδιασμένοι με το EAGLE και τα αρχεία μπορείτε να τα κατεβάσετε.

Για την κατασκευή της πλακέτας του πρώτου με τη συσκευασία PC84 χρησιμοποίησα τεχνική μεταφοράς τόνερ, με εκτυπωτή Laser που τυπώνει σε γυαλιστερό φύλλο περιοδικού και μετά το σιδερώνουμε στον χαλκό. Αναλυτικές πληροφορίες σε επόμενο άρθρο. Για την κατασκευή της πλακέτας με συσκευασία TQFP απαιτείται φωτογραφική μέθοδος που έχω παρουσιάσει σε παλιότερο άρθρο.

Στην εικόνα 1 βλέπουμε το μοντάρισμα του CPLD στην όψη των εξαρτημάτων. Επίσης υπάρχει και το head JTAG για την σύνδεση με τον programer. Στην εικόνα 2 βλέπουμε τις τέσσερις βάσεις των 20 pin για την σύνδεση με την διάτρητη πλακέτα και μερικά jumpers.

|

|

| Εικόνα 1 | Εικόνα 2 |

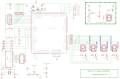

Έπειτα πρέπει να κατασκευάσουμε τον προγραμματιστή. Θα κατασκευάσουμε τον DLC-5 ο οποίος συνδέεται στην παράλληλη θύρα και η κατασκευή του είναι πολύ εύκολη. Στο σχήμα 1 βλέπουμε το ηλεκτρονικό διάγραμμα με μερικές διορθώσεις για πιο κοινά εξαρτήματα. Η θύρα πρέπει να είναι κλασική EPP-ECP και όχι αντάπτορ USB. Το καλώδιο είναι παράλληλο D25-D25 αρσενικό, όπως αυτά των παράλληλων scanners. Το flat cable που συνδέεται στη θύρα JTAG είναι 10 αγωγών με ένα παρά ένα γείωση. Καλό είναι να μην είναι μεγαλύτερο από 20-25 εκατοστά.

|

|

|

| Σχήμα 1 | Εικόνα 3 | Εικόνα 4 |

Μετά σε μια διάτρητη πλακέτα πρωτοτύπων θα κολλήσουμε τις 4 βάσεις των 20 pin και ότι άλλα εξαρτήματα χρειαστούμε για τον έλεγχο, όπως 7 segment displays, push buttons, dip switches, leds κλπ. Εγώ έβαλα και ένα 74HC4060 για παραγωγή σημάτων χρονισμού. Στην εικόνα 5 βλέπουμε τα dip switches και τα led ελέγχου. Στην εικόνα 6 φαίνεται η κάτω όψη. Προσοχή το σύρμα είναι για πηνία (με βερνίκι). Στην εικόνα 7 συνδέσαμε τον προγραμματιστή και είμαστε έτοιμοι για HDL .

|

|

|

| Εικόνα 5 | Εικόνα 6 | Εικόνα 7 |

Στις εικόνες 8, 9, 10 και 11 είναι η κατασκευή με τη συσκευασία TQFP100. Εδώ έχω 4 βάσεις dip των 24 pins η κάθε μία. Αν δεν έχετε βάσεις των 24 pins, μπορείτε να φτιάξετε ενώνοντας μια 16 pins και μία 8 pins. Η κατασκευή του τυπωμένου κυκλώματος στο σπίτι είναι αρκετά δύσκολη, όπως δύσκολη είναι και κόλληση του cpld πάνω στην πλακέτα. Συνιστώ την συσκευασία PC84.

|

|

|

|

| Εικόνα 8 | Εικόνα 9 | Εικόνα 10 | Εικόνα 11 |

Κατεβάστε εδώ τα τυπωμένα κυκλώματα σε post script και pdf αρχεία. Επίσης εδώ τα datasheets για το cpld και το 74HC125 που έχει ο προγραμματιστής.

Starter Kit

Στη διάτρητη πλακέτα μπορούμε να βάλουμε ότι εξαρτήματα θέλουμε για να ελέγχουμε την σωστή λειτουργία της λογικής του chip. Εγώ έβαλα ένα οκταπλό dip-switch, τρία push buttons, πέντε leds και τέσσερα 7 segment displays με σάρωση. Στην εικόνα 12 βλέπετε την όλη κατασκευή και στο σχήμα 2 το θεωρητικό κύκλωμα. Η xilinx συνιστά να μην κάνουμε χρήση αντιστάσεων pulldown καθώς και τα led να συνδέονται με την κάθοδο στο I/O pin. Αυτό συνεπάγεται χρήση display κοινής ανόδου. Μέσα στο πλαίσιο του διαγράμματος υπάρχει και ο εναλλακτικός τρόπος σύνδεσης των διακοπτών και leds. Βέβαια και το αρχικό σχέδιο δουλεύει καταπληκτικά. Κατεβάστε εδώ το θεωρητικό κύκλωμα σε μορφή pdf.

|

|

| Εικόνα 12 | Σχήμα 2 |

Προγραμματισμός

Για να σχεδιάσουμε την λογική του chip σε γλώσσα VHDL ή VERILOG θα πρέπει να κατεβάσουμε από την Xilinx το ISE Webpack το οποίο είναι δωρεάν. Εκτελούμε το Project Navigator κατά προτίμηση την έκδοση 32bit όπου λειτουργεί και ο simulator. Πατάμε New Project όπου δίνουμε όνομα, φάκελο αποθήκευσης και στο Top-level source type επιλέγουμε HDL. Μετά επιλέγουμε το chip και την συσκευασία που χρησιμοποιούμε, την ταχύτητα σε ns (π.χ. 15ns). Στο πεδίο simulator βάζουμς ISIM ή Modelsim αν τον έχουμε. Μετά πατάμε τρεις φορές Next και μετά Finish. Στο design και στο όνομα του chip πατάμε δεξί κλικ New source και επιλέγουμε VHDL Module. Στη συνέχεια Next δυο φορές και finish. Ας φτιάξουμε μια απλή πύλη And σε VHDL.

| ———————————————————————————- library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; —- Uncomment the following library declaration if instantiating entity simpletest is architecture Behavioral of simpletest is |

Έπειτα ορίζουμε το αρχείο UCF που περιγράφει σε ποια pin συνδέεται το κάθε σήμα:

| NET "a" LOC = "P1" ; NET "b" LOC = "P2" ; NET "x" LOC = "P71" ; |

Μετά στο Design – Implement Design και πατάμε Run. Αν όλα πάνε καλά θα βγάλει 4 πράσινα check. Μετά με το Impact φορτώνουμε το αρχείο .jed και προγραμματίζουμε το cpld. Κατεβάστε εδώ το αρχείο pdf με screenshots, οδηγίες και παραδείγματα της διαδικασίας εξομοίωσης και προγραμματισμού σε VHDL και Verilog.

| Εφαρμογή απλού απαριθμητή 4 bit με αποκωδικοποιητή BCD σε 7 segment |

(c)2010 Σταύρος Σ. Φώτογλου SV6GMP